Questões de Concurso

Sobre transistor em engenharia eletrônica

Foram encontradas 350 questões

Tais características são alcançadas pelo uso dos seguintes estágios amplificadores em série:

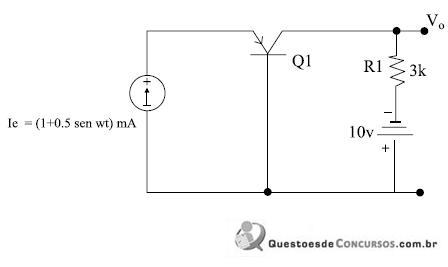

Para que este transistor opere como uma fonte de corrente, é necessário que as seguintes relações sejam satisfeitas:

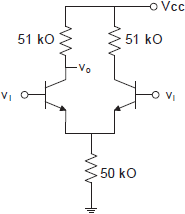

No amplificador diferencial da figura acima, os transistores apresentam fator β igual a 70 e resistência interna de base (rb) igual a 40 kΩ.

O seu ganho de modo comum vo/vi é igual a:

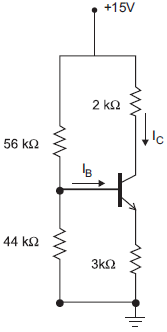

O circuito eletrônico da figura acima mostra um transistor NPN polarizado e operando na região ativa. O transistor tem, nessas condições, um ß = 100 e VBE = 0,6 V. O valor aproximado da corrente de coletor IC, em mA, é

O circuito acima representa uma porta lógica digital

implementada com a tecnologia NMOS. Os transistores de

chaveamento (com entradas

) são idênticos e do tipo

) são idênticos e do tipoenriquecimento, mas o transistor de carga é do tipo depleção. As

tensões de limiar dos transistores de chaveamento e carga são 1 V

e !3 V, respectivamente. Para esse circuito, o nível lógico alto (1

digital) é definido como qualquer tensão analógica compreendida

entre 3,5 V e 5 V, e o nível lógico baixo (0 digital) corresponde às

tensões analógicas entre 0 e 1,8 V. Esse circuito apresenta duas

peculiaridades:

I se pelo menos um dos transistores de chaveamento operar com

entrada em 5 V, a tensão de saída

não excederá 0,3 V;

não excederá 0,3 V;II somente com ambas as entradas simultaneamente no nível

lógico baixo, a saída atinge o nível lógico alto.

Com base nessas informações, julgue os itens subsequentes.

O circuito acima representa uma porta lógica digital

implementada com a tecnologia NMOS. Os transistores de

chaveamento (com entradas

) são idênticos e do tipo

) são idênticos e do tipoenriquecimento, mas o transistor de carga é do tipo depleção. As

tensões de limiar dos transistores de chaveamento e carga são 1 V

e !3 V, respectivamente. Para esse circuito, o nível lógico alto (1

digital) é definido como qualquer tensão analógica compreendida

entre 3,5 V e 5 V, e o nível lógico baixo (0 digital) corresponde às

tensões analógicas entre 0 e 1,8 V. Esse circuito apresenta duas

peculiaridades:

I se pelo menos um dos transistores de chaveamento operar com

entrada em 5 V, a tensão de saída

não excederá 0,3 V;

não excederá 0,3 V;II somente com ambas as entradas simultaneamente no nível

lógico baixo, a saída atinge o nível lógico alto.

Com base nessas informações, julgue os itens subsequentes.

O circuito acima representa uma porta lógica digital

implementada com a tecnologia NMOS. Os transistores de

chaveamento (com entradas

) são idênticos e do tipo

) são idênticos e do tipoenriquecimento, mas o transistor de carga é do tipo depleção. As

tensões de limiar dos transistores de chaveamento e carga são 1 V

e !3 V, respectivamente. Para esse circuito, o nível lógico alto (1

digital) é definido como qualquer tensão analógica compreendida

entre 3,5 V e 5 V, e o nível lógico baixo (0 digital) corresponde às

tensões analógicas entre 0 e 1,8 V. Esse circuito apresenta duas

peculiaridades:

I se pelo menos um dos transistores de chaveamento operar com

entrada em 5 V, a tensão de saída

não excederá 0,3 V;

não excederá 0,3 V;II somente com ambas as entradas simultaneamente no nível

lógico baixo, a saída atinge o nível lógico alto.

Com base nessas informações, julgue os itens subsequentes.

estiverem fixadas no nível lógico baixo, é possível que haja dissipação apreciável de potência pelo circuito.

estiverem fixadas no nível lógico baixo, é possível que haja dissipação apreciável de potência pelo circuito.No circuito eletrônico acima, que mostra um amplificador a transistor, os potenciais quiescentes de polarizações VB e VC são iguais, respectivamente, a 8 V e 12 V, e Vcc é 16 V. O ganho AC do amplificador é igual a 100 e uma fonte de sinal com impedância de entrada muito mais baixa que a impedância de entrada do amplificador injeta, em vi , uma tensão senoidal com frequência na faixa adequada do amplificador e tensão de pico a pico igual a 20 mV.

Considerando que, nesse circuito, o transistor esteja corretamente polarizado na região ativa, que as distorções do sinal amplificado sejam desprezíveis e que os capacitores têm valores de capacitância tal que, para as frequências dos sinais amplificados, eles funcionem como curto-circuito, assinale a opção correta.

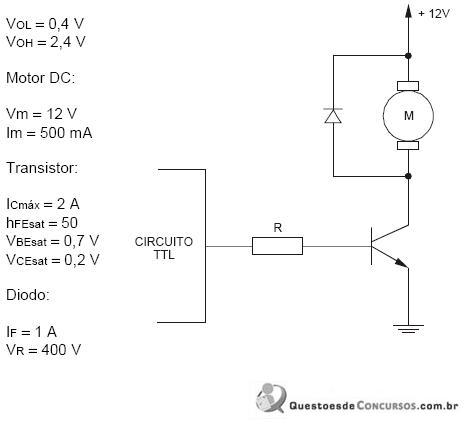

O valor comercial do resistor R que melhor satisfaz as condições do circuito é de

Nos manuais de circuitos integrados TTL essa especificação é representada por

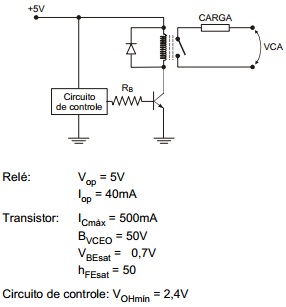

O resistor RB mais adequado para a operação da interface de potência é

do circuito mostrado?

do circuito mostrado?