Questões de Concurso

Sobre flip-flops em engenharia eletrônica

Foram encontradas 112 questões

A figura acima mostra um Flip-Flop do tipo JK mestre-escravo

com entrada preset (PR) e clear (CLR). Considerando essas

informações, julgue os itens seguintes.

A figura acima mostra um Flip-Flop do tipo JK mestre-escravo

com entrada preset (PR) e clear (CLR). Considerando essas

informações, julgue os itens seguintes.

Um encoder incremental possui dois sinais de saída, na forma de onda

quadrada, de mesma freqüência e defasados em ¼ de ciclo. Assumindo que

as saídas dos canais tenham ciclo de trabalho de 50%, existem duas

possibilidades para a temporização dos mesmos, conforme indicado por caso

A e caso B na figura acima. Os sinais do encoder incremental são

processados pelo circuito digital indicado na mesma figura. Acerca do

funcionamento desse circuito em regime permanente, e considerando que

todos os componentes do circuito são ideais, julgue os itens subseqüentes.

do Flip-flop do tipo D sempre estará em nível lógico baixo.

do Flip-flop do tipo D sempre estará em nível lógico baixo.

Um encoder incremental possui dois sinais de saída, na forma de onda

quadrada, de mesma freqüência e defasados em ¼ de ciclo. Assumindo que

as saídas dos canais tenham ciclo de trabalho de 50%, existem duas

possibilidades para a temporização dos mesmos, conforme indicado por caso

A e caso B na figura acima. Os sinais do encoder incremental são

processados pelo circuito digital indicado na mesma figura. Acerca do

funcionamento desse circuito em regime permanente, e considerando que

todos os componentes do circuito são ideais, julgue os itens subseqüentes.

sempre estará em nível alto.

sempre estará em nível alto.

Um encoder incremental possui dois sinais de saída, na forma de onda

quadrada, de mesma freqüência e defasados em ¼ de ciclo. Assumindo que

as saídas dos canais tenham ciclo de trabalho de 50%, existem duas

possibilidades para a temporização dos mesmos, conforme indicado por caso

A e caso B na figura acima. Os sinais do encoder incremental são

processados pelo circuito digital indicado na mesma figura. Acerca do

funcionamento desse circuito em regime permanente, e considerando que

todos os componentes do circuito são ideais, julgue os itens subseqüentes.

do flip-flop do tipo D sempre estará em nível lógico alto.

do flip-flop do tipo D sempre estará em nível lógico alto.

Um encoder incremental possui dois sinais de saída, na forma de onda

quadrada, de mesma freqüência e defasados em ¼ de ciclo. Assumindo que

as saídas dos canais tenham ciclo de trabalho de 50%, existem duas

possibilidades para a temporização dos mesmos, conforme indicado por caso

A e caso B na figura acima. Os sinais do encoder incremental são

processados pelo circuito digital indicado na mesma figura. Acerca do

funcionamento desse circuito em regime permanente, e considerando que

todos os componentes do circuito são ideais, julgue os itens subseqüentes.

estivesse sempre em nível alto, a porta ou-exclusivo (exclusive-Or) inverteria o sinal

estivesse sempre em nível alto, a porta ou-exclusivo (exclusive-Or) inverteria o sinal

Um encoder incremental possui dois sinais de saída, na forma de onda

quadrada, de mesma freqüência e defasados em ¼ de ciclo. Assumindo que

as saídas dos canais tenham ciclo de trabalho de 50%, existem duas

possibilidades para a temporização dos mesmos, conforme indicado por caso

A e caso B na figura acima. Os sinais do encoder incremental são

processados pelo circuito digital indicado na mesma figura. Acerca do

funcionamento desse circuito em regime permanente, e considerando que

todos os componentes do circuito são ideais, julgue os itens subseqüentes.

possui freqüência duas vezes maior que a freqüência do sinal

possui freqüência duas vezes maior que a freqüência do sinal  .

.

Considerando um sistema de comunicação digital que possua as

características mostradas na figura acima, referentes ao sinal digital e à

seqüência binária resultante, julgue os itens seguintes.

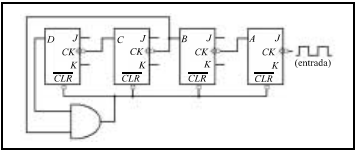

Com relação ao circuito seqüencial cujo diagrama está ilustrado acima, e considerando que os bits D, C, B e A formam um número variável binário em que D é o bit mais significativo, julgue os itens subseqüentes.

Trata-se de um contador assíncrono.