Questões de Concurso

Sobre álgebra booleana e circuitos lógicos em engenharia eletrônica em engenharia eletrônica

Foram encontradas 507 questões

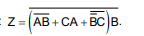

Considerando quatro variáveis binárias A, B, C e Z, assinale a alternativa que apresenta o circuito lógico que pode ser

utilizado para implementar a expressão:

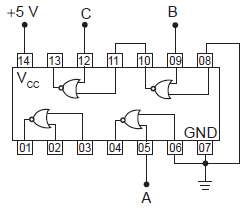

Se em determinado instante, os níveis lógicos dos sinais são: A=1, B=0 e C=0; então, os níveis lógicos das saídas nos pinos 04, 10 e 13 serão, respectivamente:

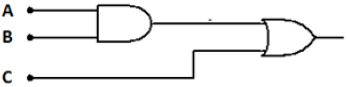

Identifique o circuito equivalente ao da imagem abaixo somente por portas NAND.

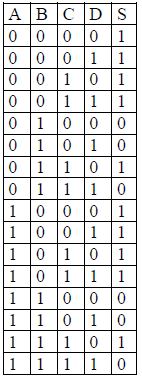

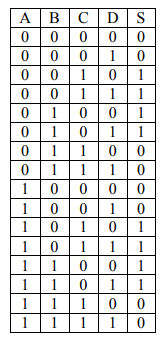

Acerca do circuito digital com entradas lógicas A, B, C e D mostrado acima e considerando que a notação X’ represente a negação da variável booleana X, julgue o item.

O circuito mostrado é classificado como sequencial por

apresentar elementos de memória.

Acerca do circuito digital com entradas lógicas A, B, C e D mostrado acima e considerando que a notação X’ represente a negação da variável booleana X, julgue o item.

A saída do circuito pode ser descrita, na forma normal

canônica conjuntiva, pela equação F = AD + B’D.

Acerca do circuito digital com entradas lógicas A, B, C e D mostrado acima e considerando que a notação X’ represente a negação da variável booleana X, julgue o item.

A saída F do circuito pode ser descrita pela equação F = D(A+B’).

Um determinado comportamento de um circuito lógico foi especificado com linguagens de descrição de hardware (HDL). Após o processo de síntese de alto nível, ferramentas computacionais determinaram um fluxo de dados (data path) e um fluxo de controle e estados (control path), usando RTL (register transfer logic), IP (intelectual property) Cores e outros recursos tecnológicos disponíveis em uma determinada arquitetura de FPGA. Foi realizada uma simulação digital pós-síntese que verificou que os resultados atenderam à especificação original. Entretanto, após a programação, o hardware real da FPGA não operou de forma correta, com falhas durante seu funcionamento.

A respeito desse processo, é correto afirmar que

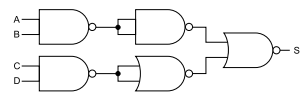

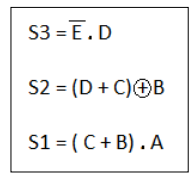

Analise o circuito digital a seguir, composto por portas lógicas.

Assinale a alternativa que relaciona corretamente a saída S com as entradas A, B, C e D.

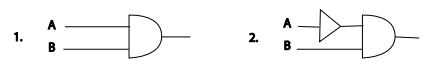

Nos circuitos lógicos abaixo, considere que A tem valor Falso e B tem valor Verdadeiro.

Qual o valor booleano final de cada circuito?

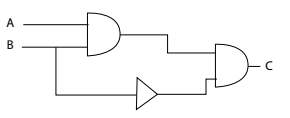

Dado o circuito lógico representado abaixo e as entradas A e B, defina a expressão representada pela saída C:

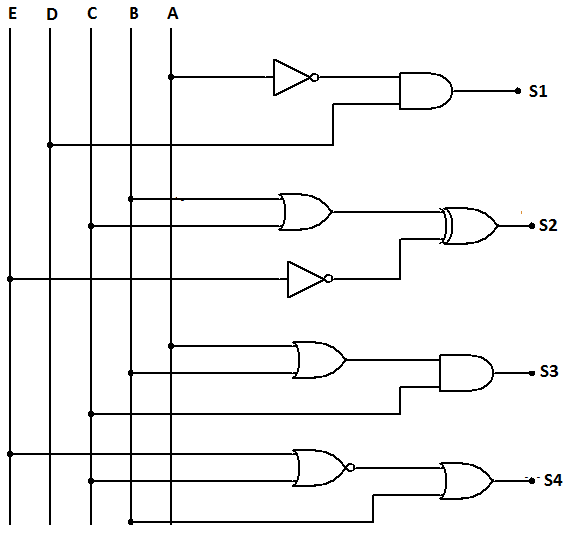

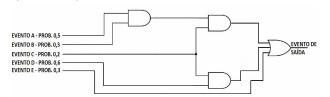

Um dado evento de saída depende dos eventos de entrada A, B, C, D e E.

A árvore de falhas a seguir, representado por lógica booleana, apresenta as probabilidades de cada um dos eventos de entrada.

A probabilidade do evento de saída acontecer é de

Considere a tabela verdade de um dado circuito digital, a seguir.

A saída Y desse circuito é:

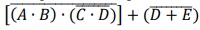

Qual das alternativas representa a expressão simplificada da saída do diagrama lógico mostrado que apresenta a seguinte

expressão Lógica  ?

?

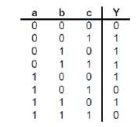

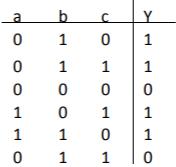

A tabela verdade abaixo apresenta o estado da saída Y em função das variáveis binárias independentes a, b e c.

A expressão de Y na 2ª forma canônica é: