Questões de Concurso

Sobre álgebra booleana e circuitos lógicos em engenharia eletrônica em engenharia eletrônica

Foram encontradas 507 questões

Um sinal de relógio de 100 MHz cadencia um circuito digital síncrono.

O maior atraso permitido para um circuito combinacional a esse sincronismo é de

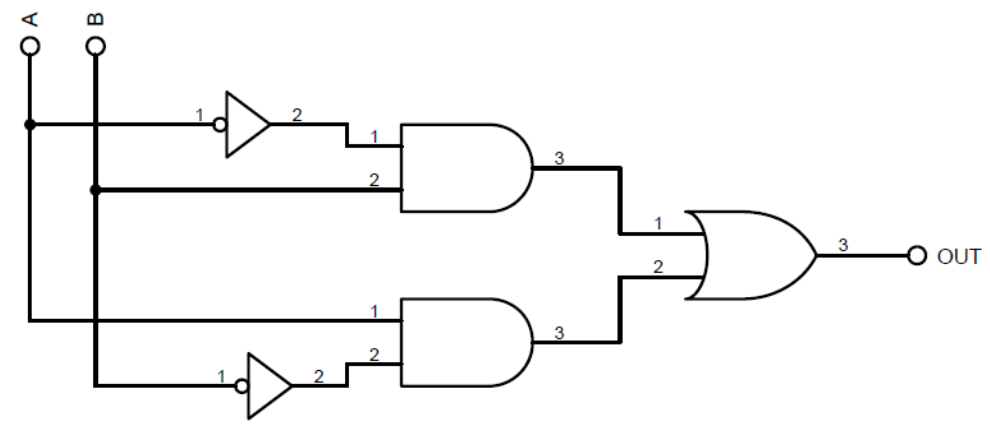

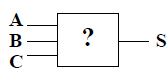

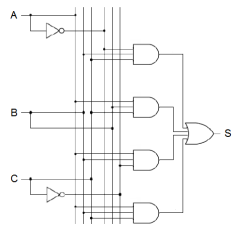

A figura a seguir apresenta um circuito lógico digital.

Considerando as entradas A, B e C, a saída em S é:

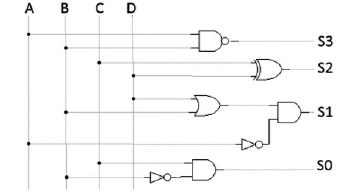

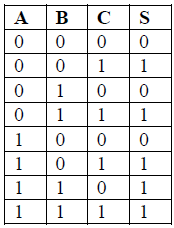

A figura a seguir apresenta a tabela verdade de um circuito digital.

A saída desse circuito é

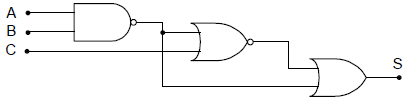

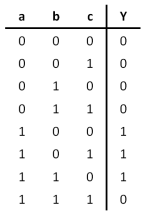

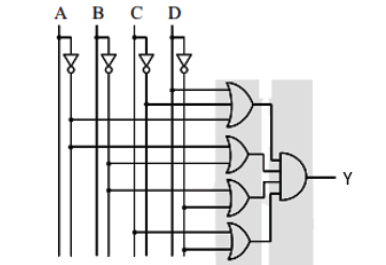

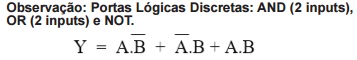

A função Y do circuito digital abaixo está corretamente descrita na alternativa:

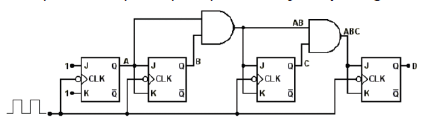

( ) Esta montagem trata de um contador assíncrono.

( ) Para transformarmos a montagem em um contador decrescente basta utilizarmos a saída Q barrada.

( ) Neste tipo de contador o atraso não depende do número de bits, mas apenas da tecnologia utilizada. Por outro lado, como o atraso de propagação é menor, o contador síncrono pode trabalhar com frequências maiores que o contador assíncrono.

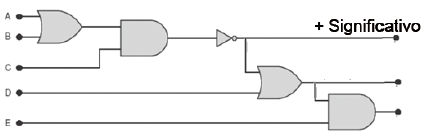

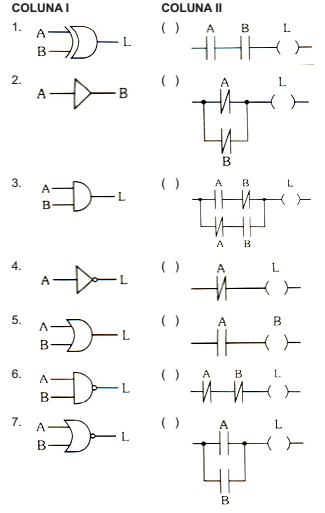

Considerando a mesma expressão da questão anterior, podemos representá-la de outra forma mais simples, considerando as portas lógicas básicas.

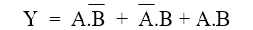

Considere a figura abaixo.

Tendo em vista a lógica binária por meio da qual os controladores lógicos programáveis operam, os símbolos apresentados por I e II, representam, correta e respectivamente:

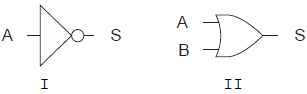

Numere a COLUNA II de acordo com a COLUNA I, associando cada uma das funções lógicas à sua correspondente na linguagem Ladder.

Assinale a sequência CORRETA.

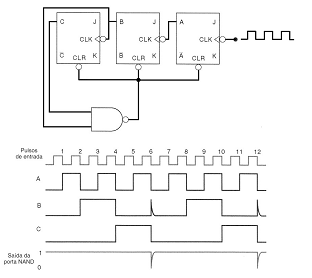

Analise o circuito a seguir, considerando que todas as entradas J e K estão em nível 1.

Com relação ao funcionamento desse circuito, é correto

afirmar:

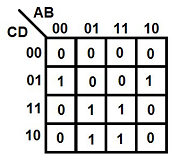

Minimize a função f (A, B, C, D) representada pelo mapa de Karnaugh a seguir.

A saída S dessa função é:

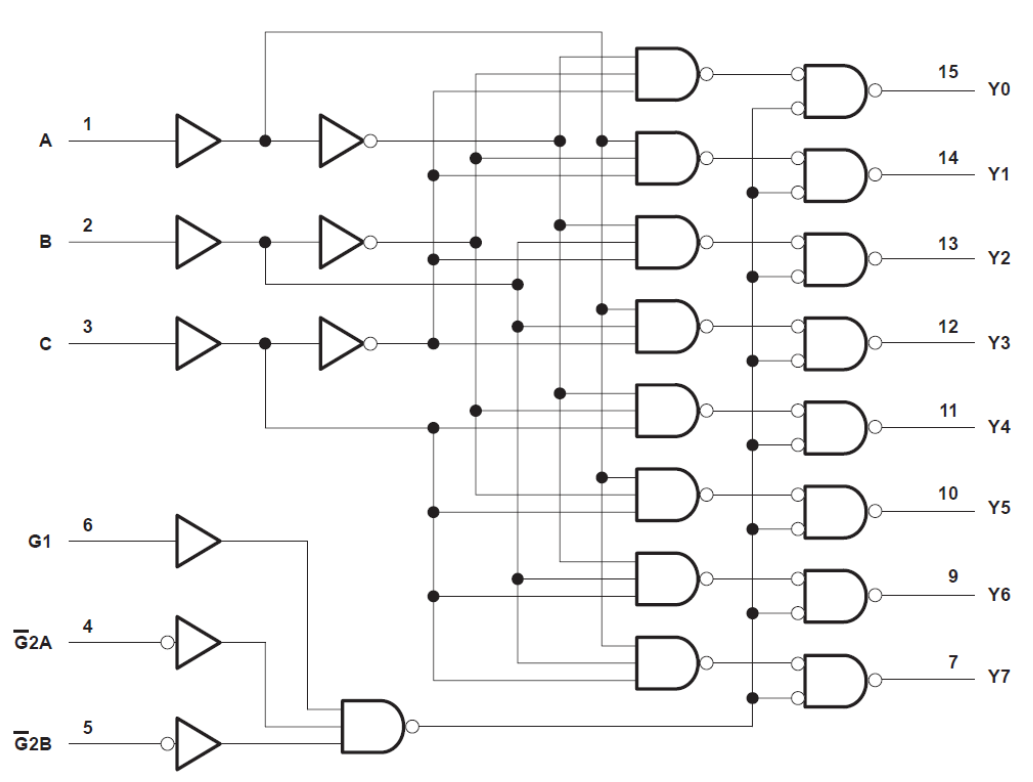

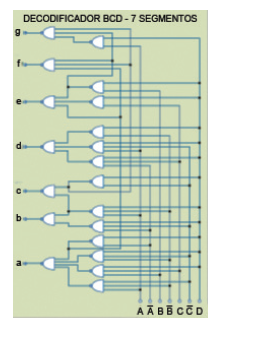

Assinale a alternativa correta em relação ao seguinte circuito lógico MSI.