Questões de Concurso Sobre flip-flops em engenharia eletrônica

Foram encontradas 111 questões

Resolva questões gratuitamente!

Junte-se a mais de 4 milhões de concurseiros!

Podemos afirmar que quando: J =0 , K = 0, clock =

Podemos afirmar que quando: J =0 , K = 0, clock =  , a saída Q será :

, a saída Q será :

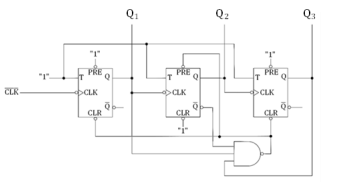

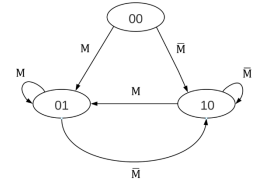

Esse contador possui a seguinte quantidade de estados estáveis:

Dado que o bit B2 será implementado utilizando um flip-flop D, a sua lógica de próximo estado pode ser expressa por