Questões Militares Sobre álgebra booleana e circuitos lógicos em engenharia eletrônica em engenharia eletrônica

Foram encontradas 133 questões

Resolva questões gratuitamente!

Junte-se a mais de 4 milhões de concurseiros!

Ano: 2020

Banca:

Marinha

Órgão:

Quadro Técnico

Prova:

Marinha - 2020 - Quadro Técnico - Quadro Técnico - Primeiro Tenente - Informática |

Q2242803

Engenharia Eletrônica

Sobre as identidades da álgebra booleana, qual opção representa uma forma da lei de DeMorgan?

Ano: 2023

Banca:

Aeronáutica

Órgão:

CIAAR

Prova:

Aeronáutica - 2023 - CIAAR - Oficial Engenheiro - Engenharia Elétrica |

Q2195682

Engenharia Eletrônica

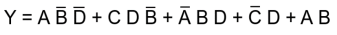

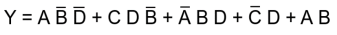

Considere a expressão booleana abaixo.

A opção que representa a expressão simplificada da equação acima é

A opção que representa a expressão simplificada da equação acima é

Ano: 2023

Banca:

Aeronáutica

Órgão:

CIAAR

Prova:

Aeronáutica - 2023 - CIAAR - Oficial Engenheiro - Engenharia Eletrônica |

Q2191628

Engenharia Eletrônica

Bits de paridade podem ser adicionados em códigos digitais para permitir a detecção e a correção dos erros que

possam ocorrer durante a transmissão e a recepção das informações binárias. Supondo que um sistema esteja

usando paridade par na transmissão de dados, o código recebido com erro de paridade no terminal remoto é

Ano: 2023

Banca:

Aeronáutica

Órgão:

CIAAR

Prova:

Aeronáutica - 2023 - CIAAR - Oficial Engenheiro - Engenharia Eletrônica |

Q2191617

Engenharia Eletrônica

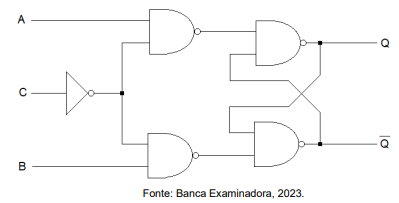

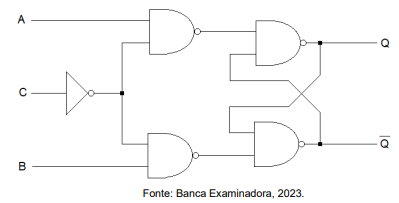

O bloco de memória mais importante na tecnologia digital, implementado a partir de portas lógicas, é o multivibrador

biestável, chamado de flip-flop. A figura abaixo mostra um tipo de flip-flop com duas entradas de dados A e B e uma

entrada de controle C.

Considerando as informações e a figura acima, quando as entradas forem A = 1, B = 0 e C = 0, a saída Q do flip-flop será

Considerando as informações e a figura acima, quando as entradas forem A = 1, B = 0 e C = 0, a saída Q do flip-flop será

Ano: 2023

Banca:

Aeronáutica

Órgão:

CIAAR

Prova:

Aeronáutica - 2023 - CIAAR - Oficial Engenheiro - Engenharia Eletrônica |

Q2191613

Engenharia Eletrônica

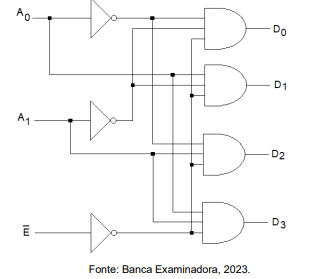

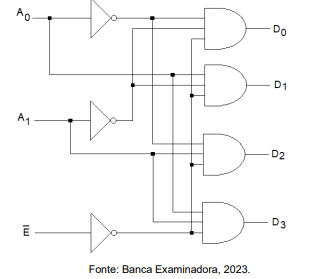

O diagrama ilustrado na figura abaixo representa um demultiplexador de duas para quatro linhas, ou duas entradas

para quatro saídas.

Considerando as informações e figura acima, quando as saídas forem D0 = 0, D1= 1, D2 = 0 e D3 = 0, as entradas E, A0, e A1 serão, respectivamente

Considerando as informações e figura acima, quando as saídas forem D0 = 0, D1= 1, D2 = 0 e D3 = 0, as entradas E, A0, e A1 serão, respectivamente