Questões Militares

Sobre flip-flops em eletrônica

Foram encontradas 29 questões

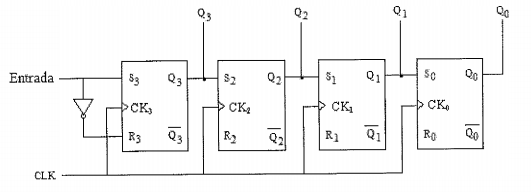

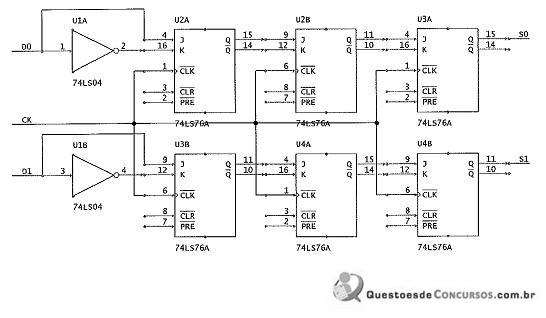

Observe a figura abaixo.

O circuito acima formado por flip-flops SR é um

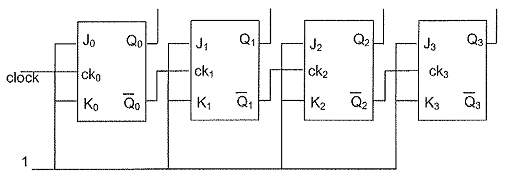

Observe a figura a seguir.

Na figura acima, 4 flip-flop tipo JK são interligados. Que

tipo de circuito sequêncial é representado por ela?

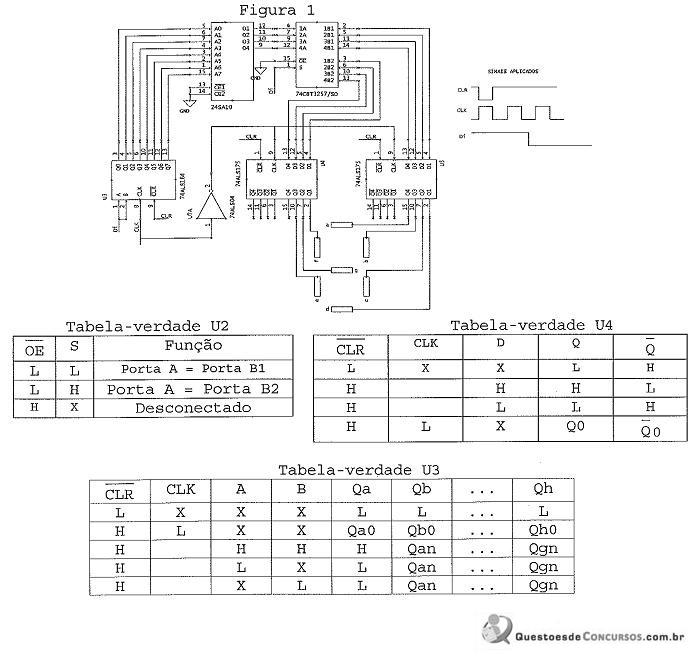

No circuito da figura 1 acima, U1 é uma memória ROM, cujas 9 primeiras palavras (em hexa) são em sequência: 4, 3, E, 5, 7, 2, 1, 0, A, e as palavras restantes são iguais a F. Além disso, a figura 1 contém as formas de onda dos sinais CLK, CLR e Di. Acima são mostradas também, as tabelas-verdade dos circuitos integrados U2, U3 e U4. Assinale a opção que contém o algarismo que ficará aceso no display de 7 segmentos após o terceiro pulso do clock.

Assinale a opção que caracteriza o circuito acima, considerando DO e D1 as entradas e so e S1 as saídas..

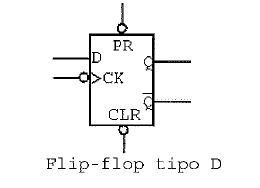

Observe a figura a seguir.

O flip-flop tipo D acima é obtido a partir de um flip-flop

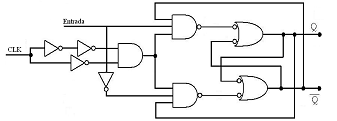

O circuito abaixo é um flip-flop____________ disparado por borda __________.

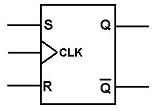

No flip flop abaixo, a entrada clock (CLK) é ativada por

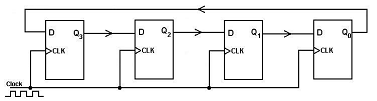

Considere que as saídas do circuito abaixo sejam inicialmente Q0 = 1 e Q1 = Q2 = Q3 = 0. Após 3 pulsos de clock, os níveis lógicos das saídas Q3, Q2, Q1 e Q0 serão, respectivamente:

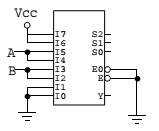

Para o MUX abaixo, qual será o valor na saída Y, quando as variáveis de seleção forem S0=1, S1=1 e S2=1?

Obs.: Considere a entrada I7 como a mais significativa e a entrada I0 como a menos significativa.