Questões Militares

Sobre circuitos lógicos e álgebra booleana em eletrônica em eletrônica

Foram encontradas 106 questões

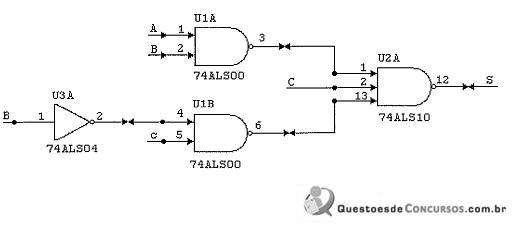

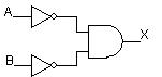

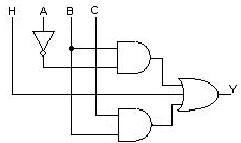

Observe o circuito lógico representado na figura abaixo.

Assinale a opção que apresenta a expressão boleana para o

circuito acima.

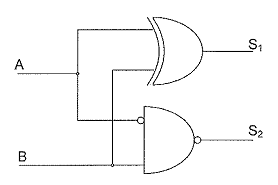

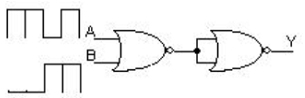

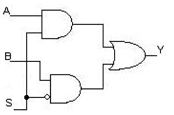

Observe a figura a seguir.

Que tipo de circuito aritmético é representado pela figura

acima?

NÍVEIS DE TENSÃO

I - VoH

II - VoL

III- ViH

IV - ViL

DESCRIÇÕES

( ) Tensão mínima que a saída da porta pode fornecer no nível alto.

( ) Tensão mínima que a entrada da porta reconhece como nível alto.

( ) Tensão mínima que a entrada da porta reconhece como nível baixo.

( ) Tensão máxima que a entrada da porta reconhece como nível baixo.

( ) Tensão máxima que a saída da porta pode fornecer no nível alto

( ) Tensão máxima que a saída da porta pode fornecer no nível baixo.

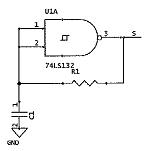

A porta lógica CMOS do circuito acima apresenta entradas Schimitt-Trigger. Em relção à funcionalidade desse circuito, é correto afirmar que a saída S

Considerando o circuito combinacional acima, assinale a opção que representa a saída S.

,center>

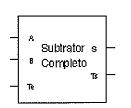

Considerando que a saída S do circuito combinacional acima implementa a seguinte função: S = A ⊕ B ⊕ Te, assinale a opção que representa a saída Ts para que o bloco seja considerado um subtrator completo.

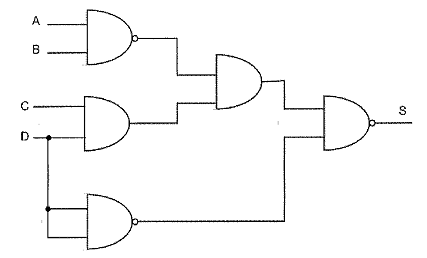

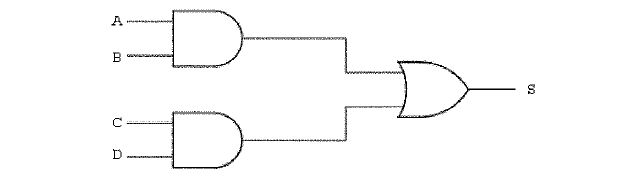

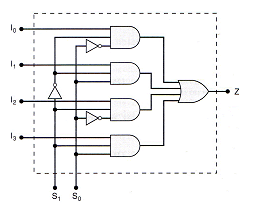

Observe a figura a seguir.

Sendo A, B, C e D as entradas do circuito lógico acima e S

sua saída, qual é a expressão booleana equivalente a esse

circuito?

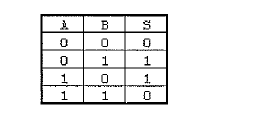

Analise a Tabela da Verdade a seguir.

Qual a função que a Tabela da Verdade acima executa?

Analise a expressão a seguir.

S= (A+ B+ C).( )

)

Como ficará a expressão booleana acima, após a simplificação?

O circuito abaixo é equivalente à porta

Qual é o sinal de saída do circuito abaixo?

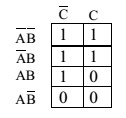

Determine a expressão simplificada para o mapa de Karnaugh abaixo.

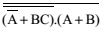

Simplificando ao máximo a expressão  obtemos

obtemos

Qual é a expressão para o diagrama abaixo?

O diagrama abaixo representa um

Em se tratando de famílias lógicas e circuitos integrados (CI), coloque (V) para verdadeiro e (F) para falso e, a seguir, assinale a alternativa que apresenta a sequência correta.

( ) A presença de um chanfro, num dos lados de um encapsulamento DIP (dual in line package), tem por finalidade possibilitar a localização do pino 1 do CI.

( ) O termo fan-out (também denominado fator de acionamento de carga) é definido como o número máximo de entradas lógicas que a saída de um circuito lógico pode acionar com segurança.

( ) Para as especificações da série TTL padrão, a tensão de entrada deve ser menor do que 0,8V ou maior do que 2,0V. Uma tensão de entrada entre 0,8 e 2,0V é considerada inválida e produzirá uma resposta de saída imprevisível, portanto tem de ser evitada.

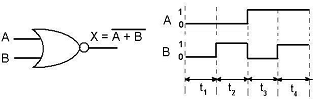

A figura abaixo representa um

Quais são os níveis lógicos na saída da porta abaixo, nos tempos t1 e t4 , respectivamente?

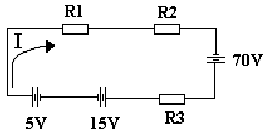

Analise a figura abaixo e calcule a corrente I, em Amperes, e as quedas de tensão, em Volts, através de R1, R2, e R3.

Dados:

R1=15Ω

R2=5 Ω

R3=10 Ω