Questões de Concurso

Sobre flip-flops em eletrônica

Foram encontradas 37 questões

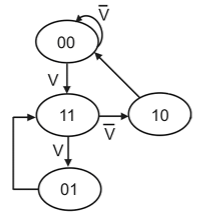

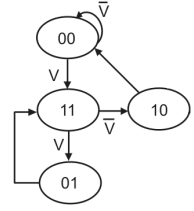

Dois flip-flops D devem implementar a sequência de estados QBQA do diagrama da figura a seguir.

A lógica de menor soma de produtos a ser usada para acionar DB é

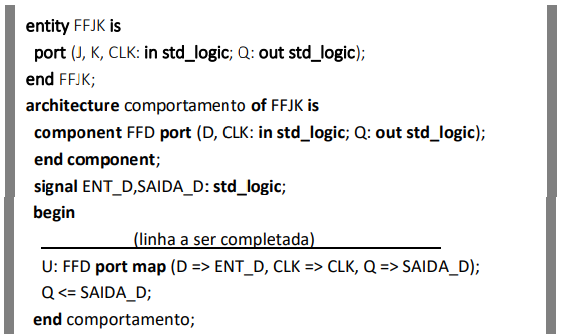

Assinale a opção que completa corretamente a linha assinalada.

A lógica de menor soma de produtos a ser usada para acionar DB é

Julgue o item seguinte, quanto a temporizadores, microprocessadores e microcontroladores.

Multivibradores monoestáveis apresentam um estado estável

e um estado não estável na saída; por sua vez, os

multivibradores astáveis apresentam dois estados não

estáveis na saída.

No que se refere a aplicações e princípios da eletrônica digital, julgue o item que segue.

O flip-flop é um dispositivo adequado para a transformação

de dados de série para dados em paralelo, enquanto o

decodificador é apropriado para a conversão do código BCD

para um display de sete segmentos.

No que se refere a aplicações e princípios da eletrônica digital, julgue o item que segue.

Considere um sistema digital, composto por flip-flops e

portas lógicas, que opere de acordo com a equação de estado

Qn+1 = D ⊕ Qn, em que D é a entrada e Qn é o estado atual.

Nesse caso, o próximo estado Qn+1 será o resultado da

operação OU entre a entrada D e o estado atual Qn.

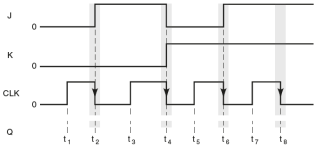

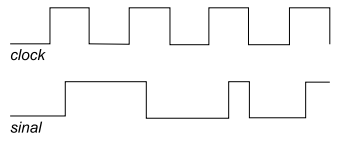

Considerando que a saída Q é iniciada em 0 e o tempo de hold do flip-flop é igual a zero, a saída Q irá comutar para 1 no instante t igual a

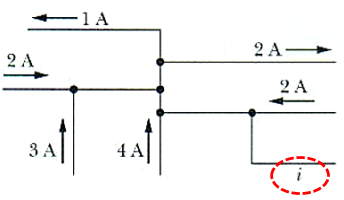

A figura a seguir mostra a distribuição das correntes em parte de um circuito elétrico.

O valor da corrente i no ramo do circuito localizado na extremidade

inferior direta indicado na figura acima é

Em relação à eletrônica digital, julgue o próximo item.

O flip-flop D é um circuito digital que pode armazenar um

bite de informação.

Assinale a alternativa que apresenta corretamente a sua saída Q.

No que se refere à eletrônica digital, julgue o item subsequente.

O uso de contadores digitais assíncronos , com grande

quantidade de flip‐flop, não é aconselhável para altas

frequências de trabalho, pois, se o atraso de

processamento de cada unidade flip‐flop for grande,

haverá erros de contagem.

Em um flip-flop JK, quando as entradas Preset e Clear estão ambas no valor lógico zero, o funcionamento desse circuito combinacional é normal

Em um flip-flop D, quando a entrada J = 0, K = 1.

Considerando os contadores formados basicamente por flip-flops, analise as seguintes afirmações.

1) Contador fornece em suas saídas um conjunto de níveis lógicos numa sequência predeterminada.

2) A velocidade da sequência gerada é determinada pela frequência dos pulsos de clock apenas para o flip-flop síncrono, já que no assíncrono não há o clock.

3) Pode-se construir um contador crescente ou decrescente, seja ele síncrono ou assíncrono.

4) Um contador pode ser construído para contar numa sequência qualquer.

Estão corretas:

Observe o flip-flop da figura abaixo e analise as proposições que se apresentam abaixo.

1) Trata-se de um flip-flop RS Síncrono.

2) Pulso de relógio (clock) determina o instante de atualização das saídas 𝑄 𝑒 𝑄̅.

3) A entrada CK (clock) inibe as entradas R e S quando seu nível lógico é 0.

4) Não existe problema de erro lógico quando R=S=1.

Estão corretas:

Process (Clk,r) Begin

If (r = ‘0’) then Q1 <= ‘0’;

Elsif (Clk’event and Clk=’1’) then Q1 <= D1;

End if;

End process;

a alternativa CORRETA que mostra o circuito descrito pelo código é: